# SONiC FD.io: Better Together

January 22, 9 a.m. PT

#### Presenters:

Miroslav Mikluš

Chief Product Officer, PANTHEON.tech

Maciek Konstantynowicz

FD.io CSIT Technical Project Lead, Distinguished Engineer, Cisco intel. partner

# What To Expect

### SONIC

- History

- Architecture

### SONiC Users

- Hyperscalers

- Enterprise

- Telco

### FD.io VPP and CSIT

- FD.io History

- VPP and CSIT Core Projects

- VPP -The "Magic" of Vectors

- FD.io CSIT and Dashboard

- CSIT Labs and Benchmarks

- FD.io CSIT Benchmark Examples

### **Motivation**

**Orchestration & Automation**

**Network operating system**

**Dataplane**

# **History of SONiC**

- : The Switch Abstraction Interface (SAI) emerged as a critical component.

- : Microsoft developed and open-sourced SONiC.

- **2017–2018**: SONiC gained traction among major cloud service providers and enterprises, including Alibaba, Tencent, and LinkedIn, for their data center operations

- : Hardware vendors contribute to SONiC, expanding compatibility and feature set.

- : The Linux Foundation announced the incorporation of SONiC into its portfolio of open networking projects.

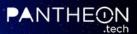

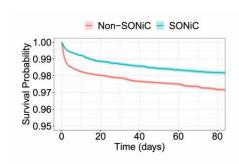

## **SONiC Architecture**

- Open-Source NOS

- Scalable

- Hardware-Agnostic

- Community-Driven

# SONiC Users: **Hyperscalers**

# **Hyperscaler: Microsoft**

**Scalability**: Microsoft built SONiC to meet the scaling and operational requirements of Azure's data center networks.

**Modular Design**: SONiC's containerized architecture allows for independent upgrades of features, enhancing flexibility and innovation while reducing issue resolution time.

**Vendor-Agnostic**: SONiC supports multivendor hardware environments via the Switch Abstraction Interface (SAI), lowering dependency on single suppliers.

#### **Key Achievements:**

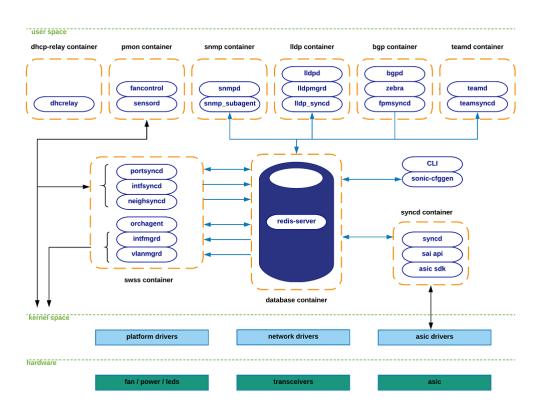

- Deployed across tens of thousands of switches in data centers globally.

- Demonstrates robustness, scalability, and multivendor interoperability.

- "Replacing vendor switch OSs with SONiC has been beneficial in improving the resilience of data center switches"

## Hyperscaler: Alibaba

Alibaba began **adopting SONiC** for its data center network devices **in 2017**.

**High Flexibility**: SONiC powers Alibaba's Al and cloud compute/storage infrastructure.

#### **Key Achievements:**

- Deployed over 100,000 white-box network devices, operating a SONiC-based software stack.

- Substantial cost savings, seamless infrastructure management, and significant scaling potential.

- **Saved 80–90% of time** of testing time by focusing efforts on features actively used on devices, rather than performing regression tests on all functionalities.

# SONiC Users: Enterprises

# **Enterprise: Walmart**

The world's largest retailer operates over **100,000 routers and switches**.

#### **Key requirements:**

- Visibility

- Reduction of operational overhead

- Vendor agnosticism

#### **Achievements:**

Successfully deployed Enterprise SONiC at scale across its data centers.

#### **Future plans:**

Expanding SONiC deployment to stores, distribution centers, campuses, and beyond...

# **Enterprise: Broadcom**

Broadcom & VMWare enterprise datacenters: ∼9 DCs worldwide

#### **Challenges Addressed:**

- Improved network visibility and troubleshooting capabilities.

- Orchestration resulted in a significant reduction in operational overhead.

- Migration from a traditional 3-tier architecture to SONiC, spine-leaf design.

- SONiC rolled out in campus and WAN environments.

# SONiC Users: Telco

### Telco: Orange

- Challenge: To reduce dependency on fully integrated products.

- Solution: Using SONiC to address the fiber access Telco Use case.

#### Key Achievements:

- Deployed 90 disaggregated open switches.

- Gained control of the features roadmap, avoiding lock-in and dependencies.

- Reduced costs, both in terms of products and power consumption.

- Attracted and upskilled talents to work in an open ecosystem.

### SONiC - FD.io

- Open-Source NOS

- Scalable

- Hardware-Agnostic

- Community-Driven

- FD.io vpp

# FD.io

**VPP Vector Packet Processing - Code and CSIT Benchmarking**

## History of FD.io

#### 2002: VPP Code Created and Used Within Cisco

The high performance network forwarding code designed and authored by Dave Barach.

#### 2004: Key Patent Contribution

Dave Barach and Eliot Dresselhaus filed a patent related to efficient packet processing.

#### 2016: VPP Goes Open Source\*

The Linux Foundation announced the Fast Data Project (FD.io) with VPP as a core component.

Cisco contributed VPP to the open-source community, enabling collaborative network innovation.

FD.io CSIT benchmarking core project created to continuously verify performance.

#### 2016+: Substantial Industry Adoption

Adoption of VPP code and CSIT benchmarking across the SW networking and multiple industry verticals

<sup>\*</sup> Cisco Blog "A BIGGER HELPING OF INTERNET PLEASE!", April 4, 2016, https://blogs.cisco.com/sp/a-bigger-helping-of-internet-please

| Cisco Systems Cisco Soure Access, Unitrella, Weber & more                                                                                       | Alibaba Cloud Alibaba Cloud  uche Netronk Virtual Functions Load Balancer                                                                         | Netgate TNSR : High-performance Secure Networking Software                                                                         | Inocybe An Open Networking Flatform                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| openstack. Openstack Clace VM (CVM) using VPP                                                                                                   | PANTHEON sech  StoneRick Enterprise - performere & mosk/ar certwoking solution                                                                    | Yahoo<br>The JP Cloud Balancer                                                                                                     | ZTE中兴<br>ZTE<br>IoT Gateway<br>MCC Platform<br>PlasS Platform                                                                                              |

| Calico/VPP dataplane An integration allowing the Calico Kulstrindes CNI to learnings VPP as its distingtions                                    | Netadvia Netadvia Netadvia Litercy-Optimised High-Fiscasincy- Financial Trading with VPP                                                          | graphiant Graphiant Vector packet processing (vPP)-based deep packet inspection (DPI) activare                                     | Mavenir  Converged packet core                                                                                                                             |

| Travelping TravelPing User Plane Gateway (UPO) based on VPP                                                                                     | Affirmed Affirmed Networks  BGON doub-native network function                                                                                     | Software for Open Networking<br>in the Cloud (SONIC)  SONIC-VPP is a platform under<br>SONIC that supports VPP data plane          | Terragraph's datapath<br>Inglementation using VPP                                                                                                          |

| EQUINIX Equinix Nation's Edge                                                                                                                   | SAMSUNG Samsung Samsung 50 UPF stack built on top of VPP                                                                                          | Exium  x Edge Data Plans achieves up to 10x pooler processing through HPP, DPD4, and SR-DV technologies                            | bignetwork Big Network |

| RTBrick RTBrick RTBrick supports VPP as a feature                                                                                               | Marvell Octoon 10  Marvell Octoon 10 DPU uses VPP hardware acceleration 50 gen us 16 Sx system level performance                                  | IPng Networks  Png Networks is a contributer to the Linux CP plugs and ouver of hi-depth betchical strictes on the VPP ecologists. | Flexiwan Flexiwan flexiwan uses VPP network stack                                                                                                          |

| VyOS and VPP - progress and plans                                                                                                               | wgtwo wgtwo Working Gloup Two uses Vector Packet Processing (VPP) to Implement this User Plane Function                                           | OpenAirtherface  OpenAir CN 50 for UPF using a VPP irreferentation                                                                 | proper GmbH (R&S)  RAS VPACE: A VPP DPI Engine Essential to Future 50 Networks                                                                             |

| SURF  At SURF, we rely on VPP as the actionary scalety for our virtual influent victors, and use A mileible (and ARM) to previous and configure | Sandya Networks Sandya Networks Sandya Networks provides highly assistate internet Connectivity with full mesh reductionsy with infancy feedings. | Lanner Electronics  Lenner partners with Floriken and Tablo Systems utilizing VPP for routing and data part.                       | TELCO SYSTEMS but will be see that a cost Telco Systems Telco Systems Edgliny OS utilizes V09 for data path.                                               |

## FD.io VPP and CSIT

### Core Projects in LFN FastData.io

| DLFNETWORKING | VPP Vector Packet Processing                                                                                        | <b>CSIT</b> Continuous System Integration and Testing                                                                                                                              |

|---------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Performance   | Feature rich networking and host stack. VPP on COTS servers in many cases <b>outperforms</b> packet processing HW¹. | Continuous <b>benchmarking</b> of VPP and DPDK.                                                                                                                                    |

| Portability   | VPP runs on COTS hardware: ARM (intel POWERS)  VPP runs in any environment: bare-metal, VM, containers.             | Performance testbeds with <b>Xeon</b> , <b>Arm</b> , <b>AMD</b> , <b>Atom</b> HW <sup>1</sup> . <b>Bare-Metal</b> , <b>VM</b> , <b>Container</b> , <b>Cloud</b> test environments. |

| Efficiency    | Allows ability to <b>upscale</b> and <b>downscale</b> .                                                             | Executing >3k benchmarking tests daily.                                                                                                                                            |

| \$ SDN        | Software <b>programmable</b> , <b>extendable</b> and <b>flexible</b> .                                              | Open-source <b>CI/CD infrastructure for benchmarking</b> of SW data-planes, <b>test data analytics</b> and <b>presentation</b> .                                                   |

<sup>1</sup> VPP optimally leverages relevant HW accelerators in NIC/DPU and in CPU socket for packet processing, I/O and memory copy operations. Some of these accelerations are benchmarked in CSIT e.g. IPsec, mem-copy, GTPU encap/decap.

### Running Networking Functions on ASICs/NPUs and COTS\* CPUs/Servers

- Purpose built ASICs/NPUs vs COTS CPUs/servers

- The former always win in terms of performance and power efficiency, if they implement what is needed ...

- But network and security requirements are moving fast and some things are hard to get right in ASICs/NPUs

- Welcome to the world of software networking on COTS CPUs/servers

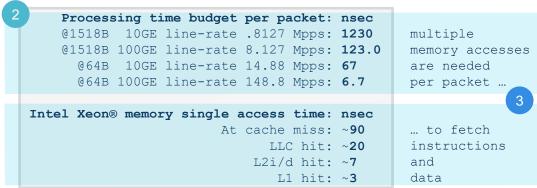

- With some hard problems to solve, one of them being the time budget per packet:

Simple and fast stuff used all the time goes into ASICs/NPUs. Complex, stateful and new service functions go into Software.

Networking in software on CPUs/Servers - some LFN FD.io references:

<sup>\*</sup> COTS - Common Off The Shelf

<sup>-</sup> Benchmarking and Analysis of Software Data Planes, 2017, https://fd.io/docs/whitepapers/performance\_analysis sw data planes dec21 2017.pdf

<sup>-</sup> Benchmarking Software Data Planes Intel® Xeon® Skylake vs. Broadwell, 2019, https://www.lfnetworking.org/wp-content/uploads/sites/55/2019/03/benchmarking\_sw\_data\_planes\_skx\_bdx\_mar07\_2019.pdf

# New "Moore's law" for Software Networking Performance Doubles Every 3 Years ...

Intel® Xeon® Icelake 10nm PCIe Gen 4.0 x16 lanes for 200 GbE per NIC slot

https://bit.ly/3PiLv9j

Intel® Xeon® Sapphire Rapids 7nm PCle Gen 5.0 x16 lanes for 400 GbE per NIC slot

Intel® Xeon® Skylake 14nm PCle Gen 3.0 x16 lanes for 100 GbE per NIC slot

https://youtu.be/aLJ0XLeV3V4

- Improving ISA, increasing PCle I/O, higher gates density (lower nm).

- Targeted Intel Xeon optimizations e.g. AES-NI crypto in Icelake<sup>(1)</sup> onwards.

And importantly optimizing software for network packets:

- Exploring and bending the laws of physics with VPP<sup>(2)</sup>.

- Enriching VPP functionality and lowering cycles per packet.

<sup>.</sup> Dio

<sup>(1)</sup> Icelake at HotChips2020, https://hc32.hotchips.org/assets/program/conference/day1/HotChips2020\_Server\_Processors\_Intel\_Irma\_ICX-CPU-final3.pdf

(2) VPP vector packet processing, cleverly batching packets into vectors for processing and solving von Neumann bottleneck.

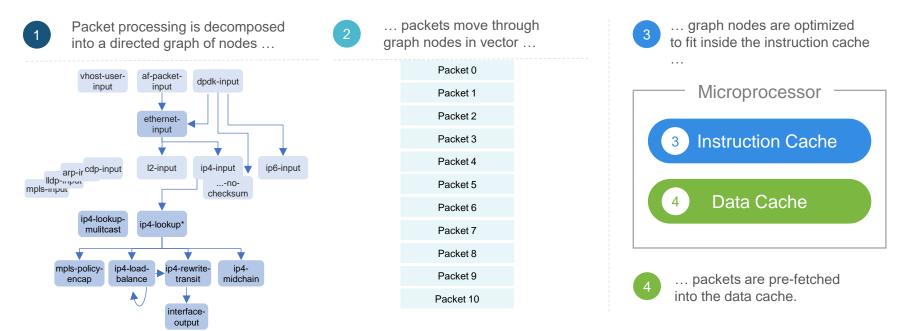

# FD.io VPP – The "Magic" of Vectors

Compute Optimized SW Network Platform

<sup>\*</sup> Each graph node implements a "micro-NF", a "micro-NetworkFunction" processing packets

Makes use of modern Processor micro-architectures.

Instruction cache & data cache always hot → Minimized memory latency and usage.

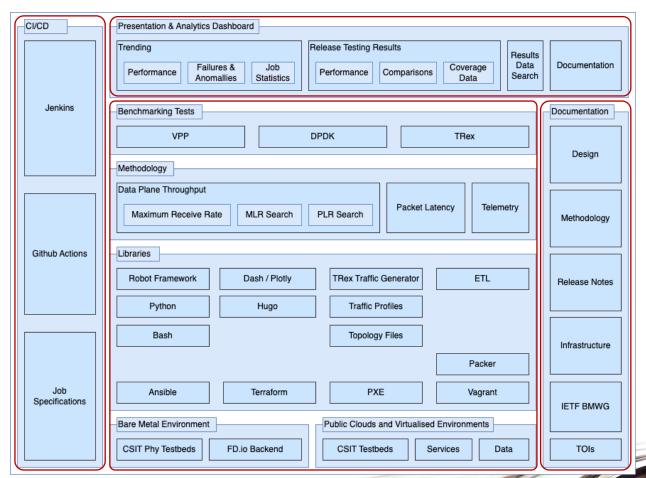

# FD.io CSIT and Dashboard

11+6

ETL pipelines

**JSON**

models

~3k

tests daily

tests weekly

~18k

~64k

performance tests per release

rls23xx

rls24xx

rls2502 (next)

optimization 32GB RAM

**Parquet** output

**250 days**

sliding window

2021 ...

... 2025

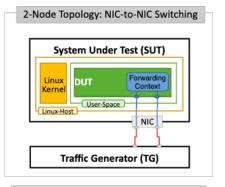

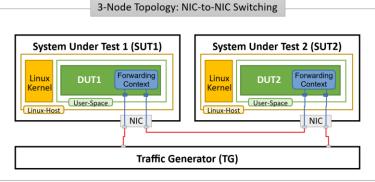

# FD.io CSIT System Design

# CSIT Benchmark Areas and Methodologies

#### **Tests**

#### **Benchmark Test Areas**

- L2 Ethernet Switching

- IPv4, IPv6 Routing

- IPsec, Wireguard with IPv4 Routing

- SRv6 Routing

- Features: ACLs, NAT44-EI/ED, Policer, ...

- IPv4. IPv6 Tunnels

- KVM VMs vHost-user

- · Docker Container Memif

- Drivers: DPDK, AVF, RDMA, AF XDP

#### **Test Methodologies**

- · Packet Throughput and Latency

- Stateful NAT44ed

- Stateful Host-stack

- Speedup Multi-Core

- Soak Tests

- Reconfiguration Tests

#### **Test Topologies**

#### **Performance Testbed Variants\***

2n-clx 2n-icx 2n-spr 2n-tx2 2n-zn2 2n-grc

2n-emr

3n-icx 3na-spr 3nb-spr 3n-alt 3n-snr 3n-icxd 3n-tsh 3n-emr 3n-oct

\*Testbed Topology – SUT Processor Model

### Performance testing: List of compute platforms

| Processor Family                                                     | Model    | Cores<br>per<br>Socket | Base<br>Frequency<br>GHz | L3 Cache<br>(LLC) MB | Testbeds                                 | NICs                                                                                                           |

|----------------------------------------------------------------------|----------|------------------------|--------------------------|----------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| EMR Intel Xeon Emerald Rapids* (on-chip HW accelerators: QAT, DSA)   | 8568Y+   | 48                     | 2.3                      | 300                  | 2 x 2n3n-emr                             | e810-2p100GE                                                                                                   |

| ICX Intel Xeon Ice Lake                                              | 8358     | 32                     | 2.6                      | 48                   | 4 x 2n-icx<br>2 x 3n-icx                 | xxv710-2p25GE, e810-4p25GE, e810-2p100GE, cx7-2p200GE<br>xxv710-2p25GE, e810-4p25GE, e810-2p100GE, cx6-2p100GE |

| <b>SPR</b> Intel Sapphire Rapids (on-chip HW accelerators: QAT, DSA) | 8462Y+   | 32                     | 2.8                      | 60                   | 2 x 2n-spr<br>1 x 3na-spr<br>1 x 3nb-spr | e810-4p25GE, e810-2p100GE, cx7-2p200GE<br>cx7-2p200GE<br>e810-4p25GE, e810-2p100GE                             |

| ZN2 AMD EPYC Zen2                                                    | 7532     | 32                     | 2.4                      | 256                  | 1 x 2n-zn2                               | x710-4p10GE, xxv710-2p25GE, cx5-2p100GE                                                                        |

| Marvell Octeon10 DPU** (Neoverse N2 cores)                           | CN106xx  | 24                     | 2.5                      | 48                   | 1 x 3n-oct                               | CN106 GSERM0 2p100GbE                                                                                          |

| ALT Ampere Altra<br>(Neoverse N1 cores)                              | Q80-30   | 80                     | 3.0                      | 32                   | 1 x 3n-alt                               | xl710-2p40GE<br>cx6-2p200GE                                                                                    |

| <b>SNR</b> Intel Atom Snowridge (on-chip HW accelerators: QAT)       | P5362B   | 24                     | 2.2                      | 27                   | 1 x 3n-snr                               | e810-4p25GE                                                                                                    |

| Nvidia Grace C1*<br>(Neoverse V2 cores)                              | C1       | 72                     | 3.3                      | 114                  | 1 x 2n-grc                               | cx5-2p100GE, cx7-2p200GbE**                                                                                    |

| ICX-D Intel Xeon Ice Lake<br>(on-chip HW accelerators: QAT)          | D-2796NT | 20                     | 2.0                      | 30                   | 1 x 3n-icxd                              | e810-XXVDA2-2p25GE                                                                                             |

<sup>\*</sup> Just added

\*\* Being added

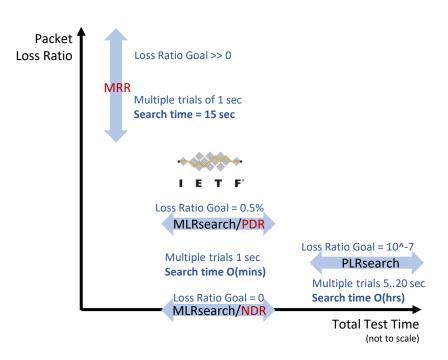

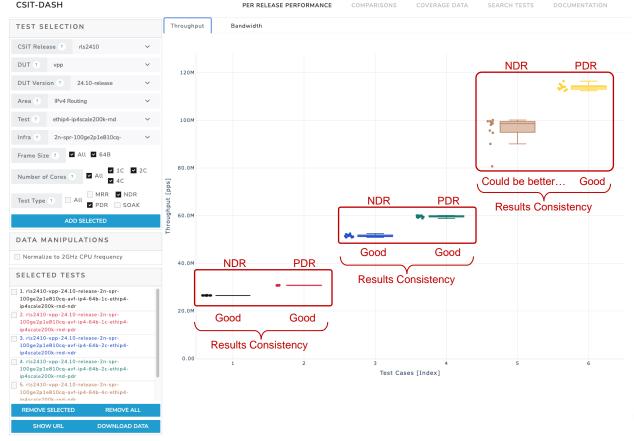

### Innovation in Test Methodologies: MRR, MLRsearch, PLRsearch

- Maximum Receive Rate (MRR)

- Measures packet throughput under maximum load regardless of packet loss.

- · Used for daily trending and automated anomaly detection in FD.io CSIT.

- Multiple Loss Ratio search (MLRsearch)

- Discovers multiple packet rates (NDR, PDR¹) in a single search.

- Discovers performance spectrum, filtering out SUT noise.

- IETF BMWG workgroup draft in Last Call: <u>draft-ietf-bmwg-mlrsearch</u>.

- Probabilistic Loss Ratio search (PLRsearch)

- Soak<sup>2</sup> testing for data planes over an extended period of time.

- IETF BMWG named draft to be updated: <u>draft-vpolak-bmwg-plrsearch</u>.

- All used in production CI for stateless and stateful benchmarks

- Stateless L2, IP4, IP6, clear-text and crypto tunnels tests for BPS, PPS.

- Stateful UDP and TCP tests for BPS, CPS, PPS, TPS.

- Why does one need MRR, PDR, NDR, Soak?

- A well behaving system should have MRR, PDR, NDR and Soak rates close to each other!

### Beyond RFC2544: Innovating in benchmarking methodologies

<sup>&</sup>lt;sup>1</sup> Packet rate and bandwidth measurements: Non-Drop Rate (NDR, with zero packet loss), ii) Partial Drop Rate (PDR, with packet loss rate not greater than configured non-zero packet-loss-ratio).

<sup>2</sup> CSIT Soak tests use PLRsearch with packet-loss-ratio set to 10^-7.

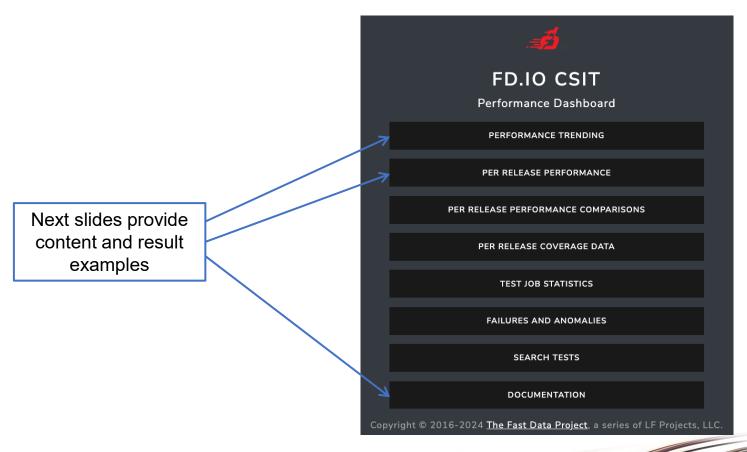

# FD.io CSIT Dashboard

https://csit.fd.io/

# FD.io CSIT – Documentation and Settings

#### CSIT-DOCS

#### **Documentation Structure**

### Search

#### Overview

CSIT-Dash CSIT

#### Methodology

Overview Measurements Tests Trending

Bisecting Per-patch Testing

#### Release Notes

CSIT rls2410 Previous

#### Infrastructure

FD.io DC Vexxhost Inventory FD.io DC Testbed Specifications FD.io DC Testbed Configuration > FD.io CSIT Testbed Versioning FD.io CSIT Logical Topologies VPP Startup Settings

#### Performance Dashboard

- 1. OVERVIEW: General introduction to CSIT Performance Dashboard and CSIT itself.

- o CSIT-Dash: The design and the structure of CSIT-Dash dashboard.

- CSIT: The design of the FD.io CSIT system, and the description of the test scenarios, test naming and test tags.

#### 2. METHODOLOGY

- Overview: Terminology, per-thread resources, multi-core speedup, VPP forwarding modes and DUT state considerations

- Measurement: Data plane throughput, packet latency and the telemetry.

- Test: Methodology of all tests used in CSIT.

- · Trending: A high-level design of a system for continuous performance measuring, trending and change detection for FD.io VPP SW data plane (and other performance tests run within CSIT sub-project).

- Per-patch Testing: A methodology similar to trending analysis is used for comparing performance before a DUT code change is merged.

- 3. RELEASE NOTES: Performance tests executed in physical FD.io testbeds.

- CSIT 24.10: The release notes of the current CSIT release.

- Previous: Archived release notes for the past releases.

#### 4. INFRASTRUCTURE

- FD.io DC Vexxhost Inventory: Physical testbeds location.

- FD.io DC Testbed Specifications: Specification of the physical testbed infrastructure.

- FD.io DC Testbed Configuration: Configuration of the physical testbed infrastructure.

- FD.io CSIT Testbed Versioning: CSIT test environment versioning to track modifications of the test environment.

- FD.io CSIT Logical Topologies: CSIT performance tests are executed on physical testbeds. Based on the packet path thru server SUTs, three distinct logical topology types are used for VPP DUT data plane testing.

- VPP Startup Settings: List of common settings applied to all tests and test dependent settings.

- 5. PERFORMANCE DASHBOARD

- Performance Trending

- Per Release Performance

- Per Release Performance Comparisons

- Per Release Coverage Data

- Test Johs Statistics

- Failures and Anomalies

- Search Tests

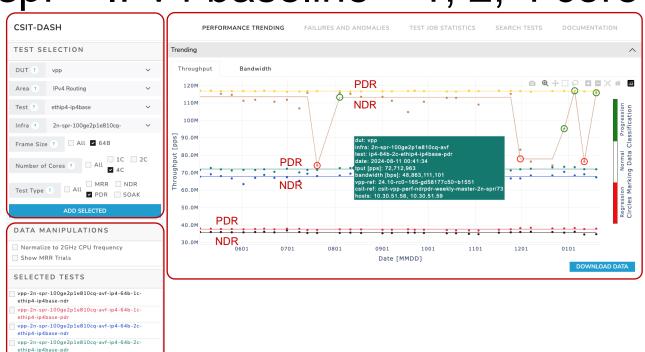

# 2n-spr – IPv4 baseline – 1, 2, 4 core

vpp-2n-spr-100ge2p1e810cq-avf-ip4-64b-4c-

ADD TELEMETRY PANEL

SHOW URL

REMOVE ALL

ethip4-ip4base-ndr

REMOVE SELECTED

https://csit.fd.io/trending/#eNrlVcsOgjAQ\_Bq8mE1oLeLFg8h\_mAqrkPBY24rBr7cYk5WDiQe54KHPmc62k0lqXWvwYLHaBlESxEkg4zL3XbDaLf3QEYFswJIBEYZnlCRwI8LsAro7QUkK1uollgN0xbDy7agtQp ObQUTuB5H86kaKjFDRM\_KxDvO1Qc0HfDGGHNq3KuPrMOtkdl22vCNT\_QMYz7wbDllsrO96ekNfb4zTJ-Nn1tEfWEe\_sE7ONHVytTJmaZOTp86NdPUqelTp2aaOvVl6qJ00bSmfv60fm6L9gbOlLqyr60HG8EFlg

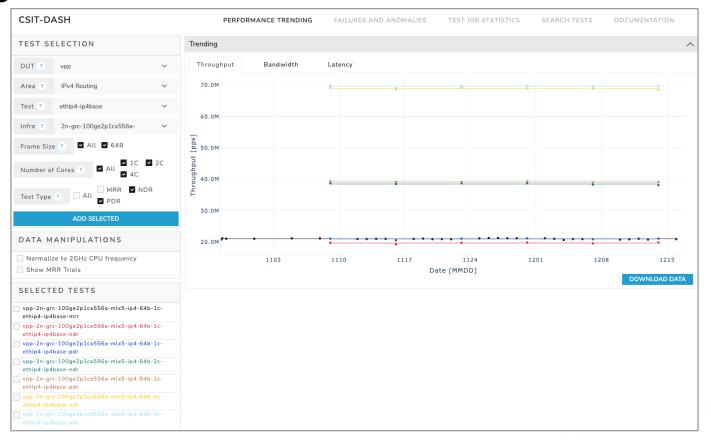

# 2n-grc – IPv4 baseline – 1, 2, 4 core

https://csit.fd.io/trending/#eNrlVssOgjAQ\_Bq8mE2ktnLyoPlfppQVSHg0bVXw6y2GZOVg4oFwgEOfszvbncyh1jUGrxbLYyDOQXQOWFSkfgr2p61fHloDqyEzCsLdLkOmQ9UKcZBQla2AQnM48ARCBejy\_uR HIi1CZUzPwi49S3p3I0pCdN4R8rsQJUiDkjJ8NYlc2q8y4\_dQ1M3ICm3xQgr1HRCuvB4EhWrM7zr9hQ5NRvEnYjrx6nQF4g1NTi6eXoN4ehLx2FKdx2ZwHluq89gMzuNLdR6fwXl8qc7jfzpPxJu6MdXny-L3Nm-e4EwhSztcvQGYblw7

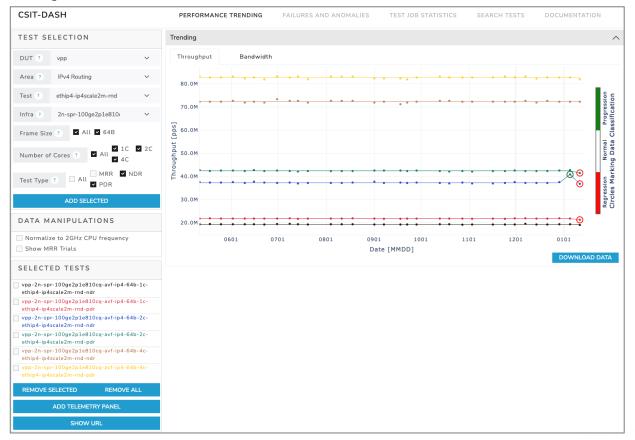

# 2n-spr – IPv4 scale2m-rnd – 1, 2, 4 core

https://csit.fd.io/trending/#eNrlVcuOwjAM\_JruZWWp8YYtFw7L8h8opIZW6sMkoavu15MiJIMEEgd6yiHPsT3xaKT40DvaempW2WKdFesMi7qMU\_b18xmXgRmwA880VJ4fCFnRUuX2CGbYQ80avvUOlAUK 1XSKw1vTELbguhK60k218HeqVZ7CXWFBuBoFeUon8caRkYTIKVAgf8Py8FUSvHemJV\_k2TEdgS3URuBlL2nCSPfoNdWi80l4t1CcjpC8juExCQcifM7EpNwJM7vSJ2EI\_X8jtRJ0FK\_6MjF5qPrXXv5vePeV\_0f BFebxl-vztUmlv4

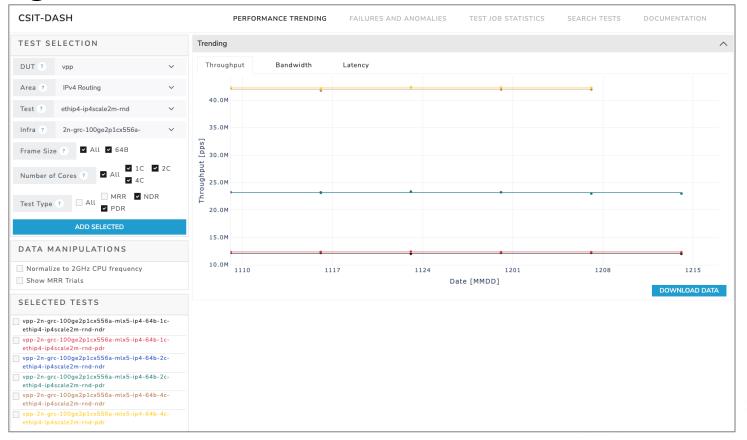

# 2n-grc – IPv4 scale2m-rnd – 1, 2, 4 core

https://csit.fd.io/trending/#eNrlVcsKwjAQ\_Jp6kYV2TezJg9r\_kliuttBHSOKjfr2pCKug4EF6ySHP2d3JDgNxvre0c9SsErU8k2CeV2GKVms52E5GwPYwdFqyNL0SGgyfZVyqaBtrhJql2Ap9pBpIF-NpzCcVg1hC7YroSvtWAy3Y7Hy5N8qM2KqgZHvfJygLCnOCKQMeXlvNB-fxcEHq1py9Y04l\_TDuA7qMJTpdxo\_mBf02WtePCL-LqWJSErzFykxDlfiBK7E0FyJE7hSxOFKMYErRRyuFD-6Uhazrrft4ycPe1f1F\_C2Vo17Xt0BTXAltg

# 2n-spr – IPv4 scale200k-rnd – 1, 2, 4 core

https://csit.fd.io/report/#eNrtVstqwzAQ\_Br3UrZIG7nupYek\_o-iypvG1HHUlWJIv75KCKxNycGQNBcd9GJG7GiHAYW4Y3oP1L0W5aqoVgVWbZOmYrF8TAt3AY1WMHgPaJ7SjqkjGwiwh-AZtFKfhF7Ti1buG-ywhtYbeDYfoB1Q3BxPaQRnO0KlvoD7BvqGjzXw7VzjT0FBm30UNMmYIAOxgBN9QvObw4hzSbXwLZOVC0m6QJHCSMyFxwl9zXZLof0huZP6IrhLrRdlu2mhePAj9Nyxqj4x\_ssnn32a6ZO\_nU-Y8zTHJ7xXnjDn6Xo-3TBPJudpjk\_mXnkyOU\_X80nyVNYP\_Y63p39fWf8CCTuxOg

# SONiC - FD.io Integration:

# Now Available!

https://github.com/sonic-net/sonic-platform-vpp

# **CSIT** Resources

#### Technical Papers

- SPR 2Tbps IPsec (2023)

- https://networkbuilders.intel.com/solutionslibrary/intel-avx-512-high-performance-ipsec-with-4th-gen-intel-xeon-scalable-processor-technology-guide

- "Benchmarking Software Data Planes Intel® Xeon® Skylake vs. Broadwell" (2019)

- https://www.lfnetworking.org/wp-content/uploads/sites/55/2019/03/benchmarking\_sw\_data\_planes\_skx\_bdx\_mar07\_2019.pdf

- "Benchmarking and Analysis of Software Data Planes" (2017)

- https://fd.io/docs/whitepapers/performance\_analysis\_sw\_data\_planes\_dec21\_2017.pdf

#### Technology Demonstrator Video Clips

- "VPP: A Terabit Secure Network Data-plane" (Intel Xeon Icelake 07-APR-2021)

- https://www.youtube.com/watch?v=ipQQmjzE g0

- "FD.io: A Universal Terabit Network Dataplane" (Intel Xeon Skylake, 11-JUL-2017)

- https://www.youtube.com/watch?v=aLJ0XLeV3V4

#### FD.io Presentations

- https://wiki.fd.io/view/Presentations

- Other FD.io Materials

- https://fd.io/

- https://fd.io/news/whitepapers/

# **CSIT** Resources

#### Project

- Wiki pages: <a href="https://wiki.fd.io/view/CSIT">https://wiki.fd.io/view/CSIT</a>

- Meetings: <a href="https://wiki.fd.io/view/CSIT/Meeting">https://wiki.fd.io/view/CSIT/Meeting</a>

- Mailing list: <a href="mailto:csit-dev@lists.fd.io">csit-dev@lists.fd.io</a>

#### CDash

Dashboard: <a href="https://csit.fd.io">https://csit.fd.io</a>

#### Source Code

- Git repo: <a href="https://git.fd.io/csit">https://git.fd.io/csit</a>

- Github mirror: <a href="https://github.com/FDio/csit">https://github.com/FDio/csit</a>

- Gerrit reviews: https://gerrit.fd.io

#### Standalone libraries

- Speeding up binary search using shorter measurements: <a href="https://pypi.org/project/MLRsearch/">https://pypi.org/project/MLRsearch/</a>

- Locating changes in time series by grouping results: <a href="https://pypi.org/project/jumpavg/">https://pypi.org/project/jumpavg/</a>

# SONiC FD.io: Better Together

January 22, 9 a.m. PT

#### Presenters:

Miroslav Mikluš

Chief Product Officer, PANTHEON.tech

Maciek Konstantynowicz

FD.io CSIT Technical Project Lead, Distinguished Engineer, Cisco intel. partner

# intel

#### **Notices & Disclaimers**

Performance varies by use, configuration and other factors.

Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See configuration disclosure for details. No product or component can be absolutely secure.

Intel optimizations, for Intel compilers or other products, may not optimize to the same degree for non-Intel products.

No product or component can be absolutely secure. Your costs and results may vary.

Intel technologies may require enabled hardware, software or service activation.

Intel does not control or audit third-party data. You should consult other sources to evaluate accuracy.

See our complete legal <u>Notices and Disclaimers</u>.

Intel is committed to respecting human rights and avoiding causing or contributing to adverse impacts on human rights. See Intel's Global Human Rights Principles.

Intel's products and software are intended only to be used in applications that do not cause or contribute to adverse impacts on human rights.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries.

Other names and brands may be claimed as the property of others.